# 262,144-word $\times$ 16-bit CMOS UV Erasable and Programmable ROM

# HITACHI

ADE-203-247A(Z) Rev. 1.0 Apr. 4, 1997

## Description

HN27C4096AHG/AHCC is a 4-Mbit ultraviolet erasable and electrically programmable ROM, featuring high speed access time and programming. Fabricated on advanced fine process and high speed circuitry technique, the HN27C4096AHG/AHCC makes high speed access time possible. Therefore, it is suitable for 16-bit microcomputer systems using high speed microcomputer such as the 80286/68020. The HN27C4096AHG/AHCC offers high speed programming using page programming mode. This device has the package variation of cerdip 40-pin and JLCC 44-pin.

#### Features

- High speed

- Access time: 85 ns (max)

- Low power dissipation

- Active mode: 35 mW/MHz (typ)

- Fast high reliability page programming and fast high-reliability programming

- Programming voltage: +12.5 V D.C.

- Programming time: 3.5 sec. (min) (Theoretical in page programming)

- Inputs and outputs TTL compatible during both read and program modes.

- Pin arrangement: 40-pin JEDEC standard, 44-pin JLCC JEDEC standard

- Device indentifier mode: Manufacturer code and device code

- Fully compatible with the HN27C4096HG/HCC Series.

#### **Ordering Information**

| Туре No.         | Access time | Package                                   |

|------------------|-------------|-------------------------------------------|

| HN27C4096AHG-85  | 85 ns       | 600-mil 40-pin Cerdip (DG-40A)            |

| HN27C4906AHCC-85 | 85 ns       | 44-pin J-bend leaded chip carrier (CC-44) |

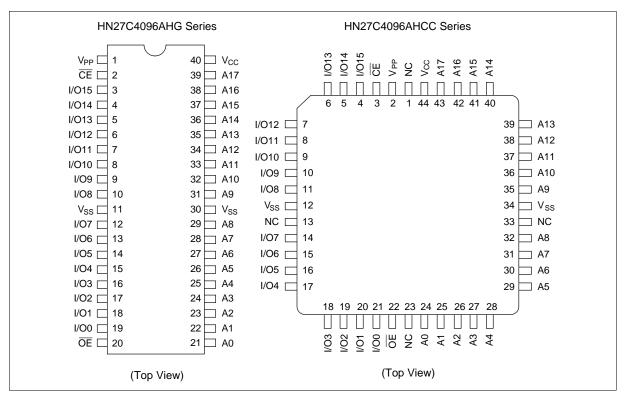

#### **Pin Arrangement**

#### **Pin Description**

| Pin name        | Function                 |

|-----------------|--------------------------|

| A0 – A17        | Address                  |

| I/O0 – I/O15    | Input/output             |

| CE              | Chip enable              |

| ŌĒ              | Output enable            |

| V <sub>cc</sub> | Power supply             |

| V <sub>PP</sub> | Programming power supply |

| V <sub>ss</sub> | Ground                   |

| NC              | No connection            |

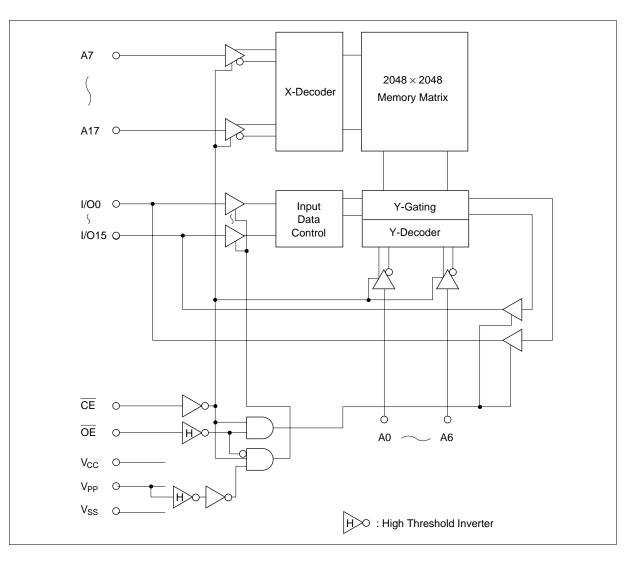

## **Block Diagram**

#### **Mode Selection**

|                | Pi              | in       | CE              | ŌE                    | A9               | V <sub>PP</sub>   | $\mathbf{V}_{cc}$ | I/O               |

|----------------|-----------------|----------|-----------------|-----------------------|------------------|-------------------|-------------------|-------------------|

|                | C               | C-44     | (3)             | (22)                  | (35)             | (2)               | (44)              | (4 – 11, 14 – 21) |

| Mode           | D               | G-40A    | (2)             | (20)                  | (31)             | (1)               | (40)              | (3 – 10, 12 – 19) |

| Read           |                 |          | $V_{IL}$        | $V_{IL}$              | х                | $V_{ss} - V_{cc}$ | $V_{cc}$          | Dout              |

| Output disable |                 |          | $V_{\rm IL}$    | $V_{\text{IH}}$       | ×                | $V_{ss} - V_{cc}$ | $V_{cc}$          | High-Z            |

| Standby        |                 |          | V <sub>IH</sub> | Х                     | ×                | $V_{ss} - V_{cc}$ | $V_{cc}$          | High-Z            |

| Page prog.     | Page program    | n set    | V <sub>IH</sub> | $V_{\rm H}^{*2}$      | ×                | V <sub>PP</sub>   | $V_{cc}$          | High-Z            |

|                | Page data late  | ch       | V <sub>IL</sub> | $V_{\rm H}^{\star 2}$ | ×                | V <sub>PP</sub>   | $V_{cc}$          | Din               |

|                | Page program    | ı        | V <sub>IL</sub> | $V_{\rm IH}$          | ×                | V <sub>PP</sub>   | $V_{cc}$          | High-Z            |

|                | Page program    | n verify | V <sub>IH</sub> | V <sub>IL</sub>       | ×                | V <sub>PP</sub>   | $V_{cc}$          | Dout              |

|                | Page program    | n reset  | V <sub>IH</sub> | $V_{\rm IH}$          | ×                | V <sub>cc</sub>   | $V_{cc}$          | High-Z            |

| Word prog.     | Program         |          | V <sub>IL</sub> | $V_{\rm IH}$          | ×                | V <sub>PP</sub>   | $V_{cc}$          | Din               |

|                | Program verify  | у        | V <sub>IH</sub> | V <sub>IL</sub>       | ×                | V <sub>PP</sub>   | $V_{cc}$          | Dout              |

|                | Optional verify | /        | V <sub>IL</sub> | V <sub>IL</sub>       | ×                | V <sub>PP</sub>   | $V_{cc}$          | Dout              |

|                | Program inhib   | oit      | V <sub>IH</sub> | $V_{\text{IH}}$       | ×                | V <sub>PP</sub>   | $V_{cc}$          | High-Z            |

| Identifier     |                 |          | V <sub>IL</sub> | $V_{\rm IL}$          | $V_{\rm H}^{*2}$ | $V_{ss} - V_{cc}$ | $V_{cc}$          | Code              |

Notes: 1. ×: Don't care.

2.  $V_{H}$ : 12.0 V ± 0.5 V

## **Absolute Maximum Ratings**

| Parameter                                   | Symbol          | Value                       | Unit |

|---------------------------------------------|-----------------|-----------------------------|------|

| All input and output voltages <sup>*1</sup> | Vin, Vout       | -0.6 <sup>*2</sup> to +7.0  | V    |

| Voltage on pin A9 and $\overline{OE}$       | V <sub>ID</sub> | -0.6 <sup>*2</sup> to +13.0 | V    |

| V <sub>PP</sub> voltage <sup>*1</sup>       | V <sub>PP</sub> | -0.6 to +13.5               | V    |

| V <sub>cc</sub> voltage <sup>*1</sup>       | V <sub>cc</sub> | -0.6 to +7.0                | V    |

| Operating temperature range                 | Topr            | 0 to +70                    | °C   |

| Storage temperature range <sup>*3</sup>     | Tstg            | -65 to +125                 | °C   |

| Storage temperature under bias              | Tbias           | -20 to +80                  | °C   |

Notes: 1. Relative to  $V_{ss}$ .

2. Vin, Vout,  $V_{ID}$  min = -2.0 V for pulse width  $\leq$  20 ns

3. Storage temperature range of device before programming.

#### Parameter Symbol Min Тур Max Unit **Test conditions** 12 Vin = 0 VInput capacitance Cin \_ pF pF Vout = 0 VOutput capacitance Cout 20 \_\_\_\_ —

#### **Capacitance** (Ta = $25^{\circ}$ C, f = 1 MHz)

#### **Read Operation**

| <b>DC Characteristics</b> ( $V_{CC}$ = | $5 V \pm 10\%$ , | $V_{PP} = V_{SS}$ to | $V_{\rm CC},  {\rm Ta} = 0 \text{ to } +70^{\circ}{\rm C})$ |

|----------------------------------------|------------------|----------------------|-------------------------------------------------------------|

|----------------------------------------|------------------|----------------------|-------------------------------------------------------------|

| Parameter                         | Symbol           | Min    | Тур | Max                               | Unit | Test conditions           |

|-----------------------------------|------------------|--------|-----|-----------------------------------|------|---------------------------|

| Input leakage current             | I <sub>LI</sub>  | _      |     | 2                                 | μΑ   | Vin = 5.5 V               |

| Output leakage current            | I <sub>LO</sub>  | _      |     | 2                                 | μΑ   | Vout = 5.5 V/0.45 V       |

| V <sub>PP</sub> current           | I <sub>PP1</sub> | _      | 1   | 20                                | μΑ   | V <sub>PP</sub> = 5.5 V   |

| Standby $V_{cc}$ current          | I <sub>SB</sub>  | _      | _   | 30                                | mA   | $\overline{CE} = V_{H}$   |

| Operating V <sub>cc</sub> current | I <sub>CC1</sub> | _      |     | 30                                | mA   | lout = 0 mA, f = 1 MHz    |

|                                   | I <sub>CC2</sub> | _      |     | 140                               | mA   | lout = 0 mA, f = 11.8 MHz |

| Input voltage                     | V <sub>IL</sub>  | -0.3*1 | _   | 0.8                               | V    |                           |

|                                   | V <sub>IH</sub>  | 2.2    | —   | V <sub>cc</sub> + 1 <sup>*2</sup> | V    |                           |

| Output voltage                    | V <sub>oL</sub>  | _      | _   | 0.45                              | V    | I <sub>oL</sub> = 2.1 mA  |

|                                   | V <sub>OH</sub>  | 2.4    |     |                                   | V    | I <sub>OH</sub> = -400 μA |

Notes: 1.  $V_{IL}$  min = -1.0 V for pulse width  $\leq$  50 ns

$V_{IL}$  min = -2.0 V for pulse width  $\leq$  20 ns

2.  $V_{IH}$  max =  $V_{CC}$  +1.5 V for pulse width  $\leq$  20 ns

If  $V_{\mbox{\tiny H}}$  is over the specified maximum value, read operation cannot be guaranteed.

## AC Characteristics ( $V_{CC} = 5 \text{ V} \pm 10\%$ , $V_{PP} = V_{SS}$ to $V_{CC}$ , Ta = 0 to $+70^{\circ}$ C)

#### **Test Conditions**

- Input pulse levels: 0.45 to 2.4 V

- Input rise and fall time:  $\leq 10$  ns

- Output load: 1 TTL gate +100 pF

- Reference levels for measuring timing: 1.5 V

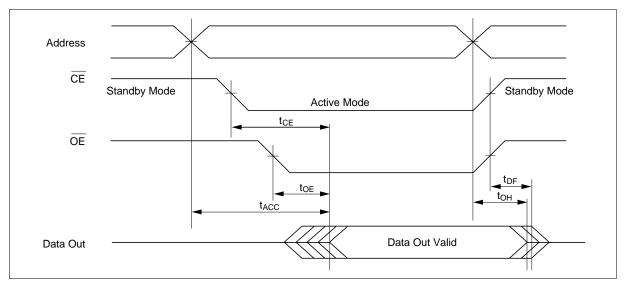

|                                       |                  | HN27C40 | 96AHG/AHCC-85 |      |                                          |

|---------------------------------------|------------------|---------|---------------|------|------------------------------------------|

| Parameter                             | Symbol           | Min     | Max           | Unit | Test conditions                          |

| Address to output delay               | t <sub>ACC</sub> | _       | 85            | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |

| CE to output delay                    | t <sub>ce</sub>  | —       | 85            | ns   | $\overline{OE} = V_{\mu}$                |

| OE to output delay                    | t <sub>oe</sub>  | —       | 45            | ns   | $\overline{CE} = V_{IL}$                 |

| OE high to output float <sup>*1</sup> | t <sub>DF</sub>  | 0       | 30            | ns   | $\overline{CE} = V_{IL}$                 |

| Address to output hold                | t <sub>он</sub>  | 5       |               | ns   | $\overline{CE} = \overline{OE} = V_{IL}$ |

Note: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

### **Read Timing Waveform**

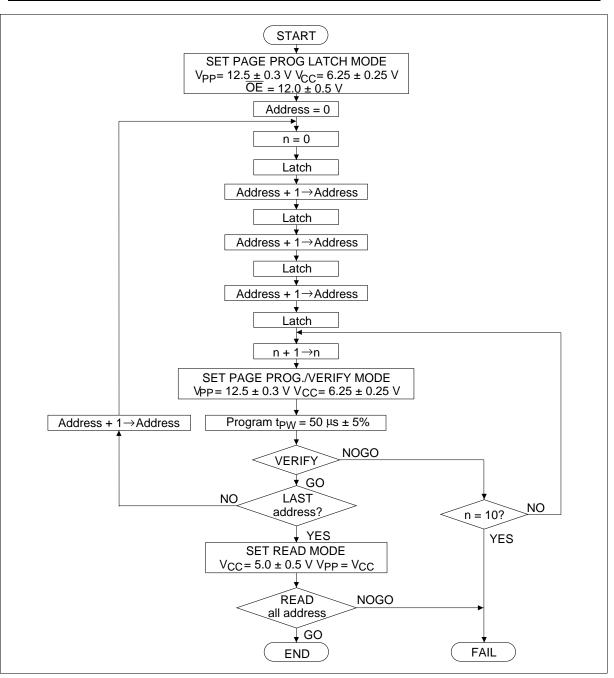

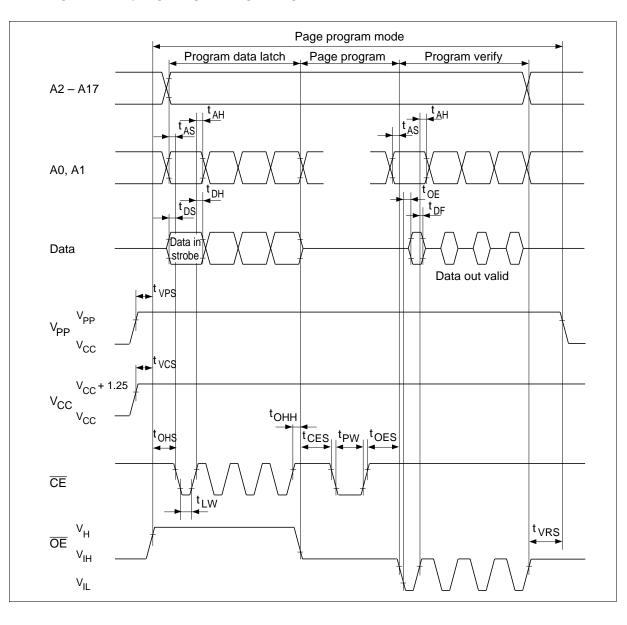

#### Fast High-Reliability Page Programming

This device can be applied the high performance page programming algorithm shown in the following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

#### Page Program Set

Apply 12 V to  $\overline{OE}$  pin after applying 12.5 V to V<sub>PP</sub> to set a page program mode.

The device operates in a page program mode until reset.

#### Page Program Reset

Set  $V_{PP}$  to  $V_{CC}$  level or less to reset a page program mode.

| Parameter                      | Symbol          | Min    | Тур  | Max                   | Unit           | Test conditions          |

|--------------------------------|-----------------|--------|------|-----------------------|----------------|--------------------------|

| Input leakage current          | I <sub>LI</sub> | _      | _    | 2                     | μΑ             | Vin = 6.5 V/0.45 V       |

| Output voltage during verify   | V <sub>OL</sub> | —      | —    | 0.45                  | V              | I <sub>OL</sub> = 2.1 mA |

|                                | V <sub>OH</sub> | 2.4    | _    | _                     | V              | $I_{OH} = -400 \ \mu A$  |

| Operating $V_{cc}$ current     | I <sub>cc</sub> | _      | —    | 50                    | mA             |                          |

| Input voltage                  | V <sub>IL</sub> | -0.1*5 | —    | 0.8                   | V              |                          |

|                                | V <sub>IH</sub> | 2.2    | —    | V <sub>cc</sub> + 0.5 | <sup>6</sup> V |                          |

|                                | V <sub>H</sub>  | 11.5   | 12.0 | 12.5                  | V              |                          |

| V <sub>PP</sub> supply current | I <sub>PP</sub> | _      | _    | 70                    | mA             | $\overline{CE} = V_{IL}$ |

**DC Characteristics** ( $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ ,  $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ ,  $Ta = 25^{\circ}C \pm 5^{\circ}C$ )

Notes: 1.  $V_{\rm CC}$  must be applied before  $V_{\scriptscriptstyle PP}$  and removed after  $V_{\scriptscriptstyle PP}.$

2.  $V_{PP}$  must not exceed 13.5 V including overshoot.

3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP}$  = 12.5 V.

4. Do not alter  $V_{PP}$  either  $V_{IL}$  to 12.5 V or 12.5 V to  $V_{IL}$  when  $\overline{CE}$  = low.

5.  $V_{IL}$  min = -0.6 V for pulse width  $\leq$  20 ns.

6. If  $V_{\mu}$  is over the specified maximum value, programming operation cannot be guaranteed.

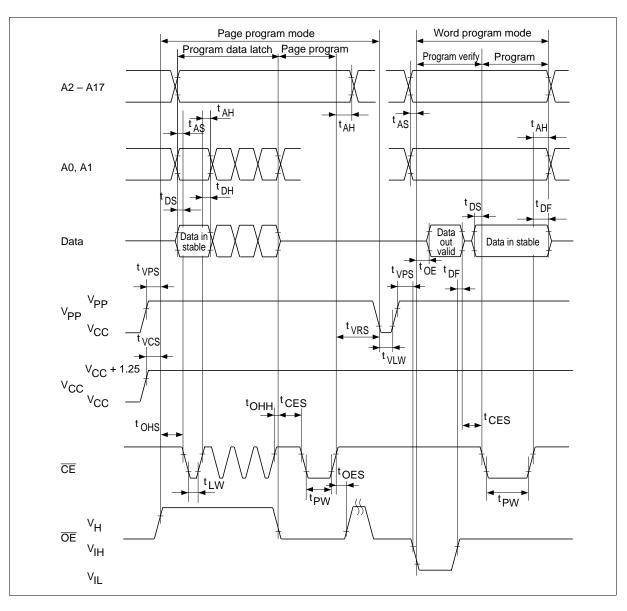

#### AC Characteristics ( $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ , $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ , $Ta = 25^{\circ}C \pm 5^{\circ}C$ )

#### **Test Conditions**

- Input pulse levels: 0.45 to 2.4 V

- Input rise and fall time:  $\leq 20$  ns

- Reference levels for measuring timings: Inputs; 0.8 V, 2.0 V

Outputs; 0.8 V, 2.0 V

| Parameter                               | Symbol             | Min  | Тур  | Max  | Unit | Test conditions |

|-----------------------------------------|--------------------|------|------|------|------|-----------------|

| Address setup time                      | t <sub>AS</sub>    | 2    | _    | _    | μs   |                 |

| OE setup time                           | t <sub>OES</sub>   | 2    | _    | _    | μs   |                 |

| Data setup time                         | t <sub>DS</sub>    | 2    | _    | _    | μs   |                 |

| Address hold time                       | t <sub>AH</sub>    | 0    | _    | _    | μs   |                 |

| Data hold time                          | t <sub>DH</sub>    | 2    | _    | _    | μs   |                 |

| OE high to output float delay           | t <sub>DF</sub> *1 | 0    | _    | 130  | ns   |                 |

| V <sub>PP</sub> setup time              | t <sub>vPS</sub>   | 2    | _    | _    | μs   |                 |

| V <sub>cc</sub> setup time              | t <sub>vcs</sub>   | 2    | _    | _    | μs   |                 |

| CE programming pulse width              | t <sub>PW</sub>    | 47.5 | 50.0 | 52.5 | μs   |                 |

| CE setup time                           | t <sub>CES</sub>   | 2    | _    | _    | μs   |                 |

| Data valid from $\overline{OE}$         | t <sub>oe</sub>    | 0    | _    | 150  | ns   |                 |

| CE pulse width during data latch        | t <sub>LW</sub>    | 1    | _    | _    | μs   |                 |

| $\overline{OE}=V_{H}$ setup time        | t <sub>OHS</sub>   | 2    | _    | _    | μs   |                 |

| $\overline{OE}=V_{H}$ hold time         | t <sub>ohh</sub>   | 2    | _    | _    | μs   |                 |

| V <sub>PP</sub> hold time <sup>*2</sup> | t <sub>vrs</sub>   | 1    | _    | _    | μs   |                 |

Notes: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

2. Page program mode will be reset when V<sub>PP</sub> is set to V<sub>cc</sub> or less.

#### Fast High-Reliability Page Programming Timing Waveform

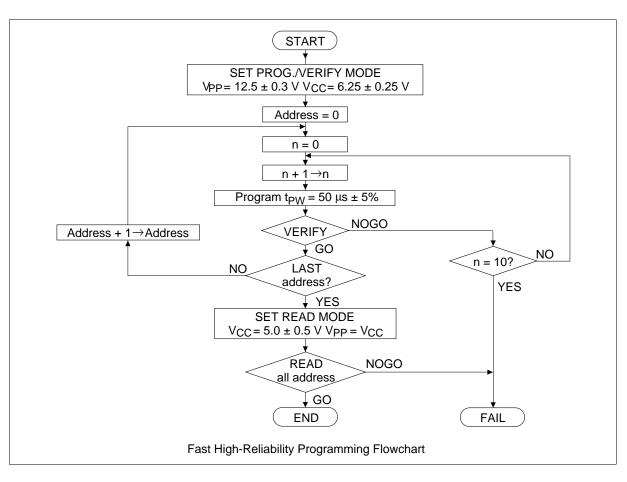

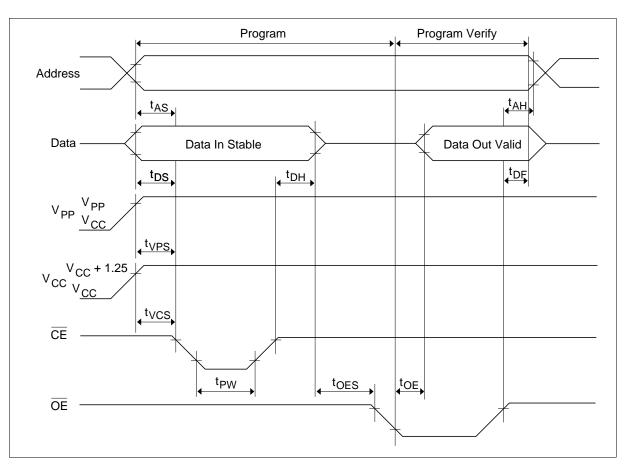

## Fast High-Reliability Programming

This device can be applied the fast high-reliability programming algorithm shown in the following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

| Parameter                         | Symbol          | Min    | Тур | Max                                 | Unit | Test conditions           |

|-----------------------------------|-----------------|--------|-----|-------------------------------------|------|---------------------------|

| Input leakage current             | I <sub>LI</sub> | _      | _   | 2                                   | μA   | Vin = 6.5 V/0.45 V        |

| V <sub>PP</sub> supply current    | I <sub>PP</sub> | _      | _   | 40                                  | mA   | $\overline{CE} = V_{IL}$  |

| Operating V <sub>cc</sub> current | I <sub>cc</sub> |        | _   | 50                                  | mA   |                           |

| Input voltage                     | V <sub>IL</sub> | -0.1*5 | _   | 0.8                                 | V    |                           |

|                                   | V <sub>IH</sub> | 2.2    | _   | V <sub>cc</sub> + 0.5 <sup>*6</sup> | V    |                           |

| Output voltage                    | V <sub>OL</sub> |        | _   | 0.45                                | V    | I <sub>oL</sub> = 2.1 mA  |

|                                   | V <sub>OH</sub> | 2.4    | _   | _                                   | V    | I <sub>OH</sub> = -400 μA |

## **DC Characteristics** ( $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ , $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ , $Ta = 25^{\circ}C \pm 5^{\circ}C$ )

Notes: 1.  $V_{cc}$  must be applied before  $V_{PP}$  and removed after  $V_{PP}$ .

2.  $V_{PP}$  must not exceed 13.5 V including overshoot.

3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP} = 12.5 \text{ V}$ .

4. Do not alter  $V_{PP}$  either  $V_{IL}$  to 12.5 V or 12.5 V to  $V_{IL}$  when  $\overline{CE}$  = low.

5.  $V_{IL}$  min = -0.6 V for pulse width  $\leq$  20 ns.

6. If V<sub>IH</sub> is over the specified maximum value, programming operation cannot be guaranteed.

#### AC Characteristics ( $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ , $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ , $Ta = 25^{\circ}C \pm 5^{\circ}C$ )

#### **Test Conditions**

- Input pulse levels: 0.45 to 2.4 V

- Input rise and fall time:  $\leq 20$  ns

- Reference levels for measuring timings: Inputs: 0.8 V, 2.0 V

Outputs: 0.8 V, 2.0 V

| Parameter                       | Symbol             | Min  | Тур  | Max  | Unit | Test conditions |

|---------------------------------|--------------------|------|------|------|------|-----------------|

| Address setup time              | t <sub>AS</sub>    | 2    | _    | _    | μs   |                 |

| OE setup time                   | t <sub>OES</sub>   | 2    | _    | _    | μs   |                 |

| Data setup time                 | t <sub>DS</sub>    | 2    | —    | —    | μs   |                 |

| Address hold time               | t <sub>AH</sub>    | 0    | _    | —    | μs   |                 |

| Data hold time                  | t <sub>DH</sub>    | 2    | _    | —    | μs   |                 |

| OE to output float delay        | t <sub>DF</sub> *1 | 0    | _    | 130  | ns   |                 |

| V <sub>PP</sub> setup time      | t <sub>VPS</sub>   | 2    | _    | —    | μs   |                 |

| V <sub>cc</sub> setup time      | t <sub>vcs</sub>   | 2    | _    | —    | μs   |                 |

| CE programming pulse width      | t <sub>PW</sub>    | 47.5 | 50.0 | 52.5 | μs   |                 |

| Data valid from $\overline{OE}$ | t <sub>oe</sub>    | 0    | _    | 150  | ns   |                 |

Note: 1. t<sub>DF</sub> is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

#### Fast High-Reliability Programming Timing Waveform

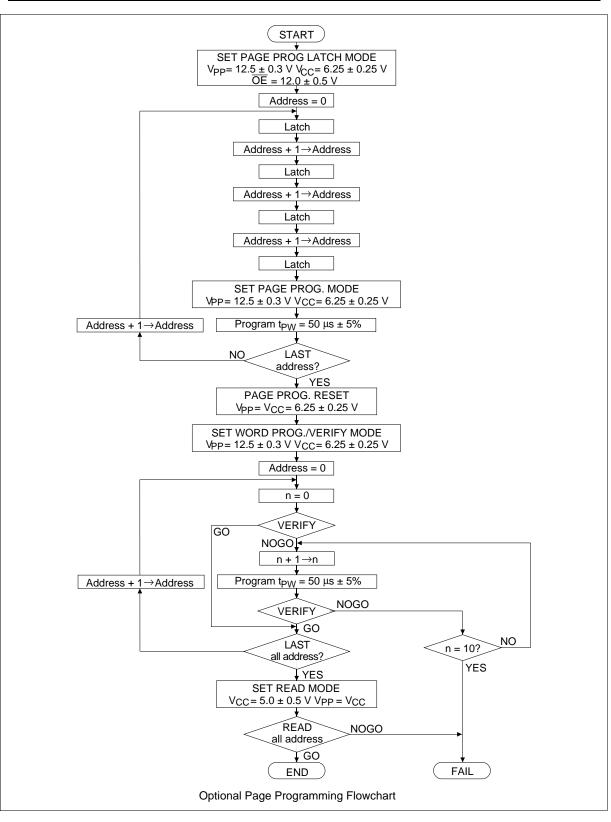

#### **Optional Page Programming**

This device can be applied the optional page programming algorithm shown in the following flowchart. This algorithm allows to obtain faster programming time without any voltage stress to the device nor deterioration in reliability of programmed data.

This programming algorithm is the combination of page programming and word verify. It can avoid the increase of programming verify time when a programmer with slow machine cycle is used, and shorten the total programming time.

Regarding the timing specifications for page programming and word verify, please refer to the specifications for fast high-reliability page programming and fast high-reliability programming.

| Parameter                         | Symbol          | Min                | Тур  | Мах                                 | Unit | Test conditions           |

|-----------------------------------|-----------------|--------------------|------|-------------------------------------|------|---------------------------|

| Input leakage current             | I <sub>U</sub>  | _                  | _    | 2                                   | μΑ   | Vin = 6.5 V/0.45 V        |

| Output voltage during verify      | V <sub>OL</sub> | —                  | _    | 0.45                                | V    | I <sub>oL</sub> = 2.1 mA  |

|                                   | V <sub>OH</sub> | 2.4                | _    | _                                   | V    | I <sub>OH</sub> = -400 μA |

| Operating V <sub>cc</sub> current | I <sub>cc</sub> | _                  | _    | 50                                  | mA   |                           |

| Input voltage                     | V <sub>IL</sub> | -0.1 <sup>*5</sup> | _    | 0.8                                 | V    |                           |

|                                   | V <sub>IH</sub> | 2.2                | _    | V <sub>cc</sub> + 0.5 <sup>*6</sup> | ° V  |                           |

|                                   | V <sub>H</sub>  | 11.5               | 12.0 | 12.5                                | V    |                           |

| V <sub>PP</sub> supply current    | I <sub>PP</sub> |                    |      | 70                                  | mA   | $\overline{CE} = V_{IL}$  |

**DC Characteristics** ( $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ ,  $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ ,  $Ta = 25^{\circ}C \pm 5^{\circ}C$ )

Notes: 1.  $V_{cc}$  must be applied before  $V_{PP}$  and removed after  $V_{PP}$ .

2.  $V_{PP}$  must not exceed 13.5 V including overshoot.

3. An influence may be had upon device reliability if the device is installed or removed while  $V_{PP}$  = 12.5 V.

4. Do not alter V\_{PP} either V\_{IL} to 12.5 V or 12.5 V to V\_{IL} when  $\overline{CE}$  = low.

5.  $V_{IL}$  min = -0.6 V for pulse width  $\leq$  20 ns.

6. If  $V_{\text{IH}}$  is over the specified maximum value, programming operation cannot be guaranteed.

#### AC Characteristics ( $V_{CC} = 6.25 \text{ V} \pm 0.25 \text{ V}$ , $V_{PP} = 12.5 \text{ V} \pm 0.3 \text{ V}$ , $Ta = 25^{\circ}C \pm 5^{\circ}C$ )

#### **Test Conditions**

- Input pulse levels: 0.45 to 2.4 V

- Input rise and fall time:  $\leq 20$  ns

- Reference levels for measuring timing: Inputs: 0.8 V, 2.0 V,

Outputs: 0.8 V, 2.0 V

| Parameter                               | Symbol                        | Min  | Тур  | Max  | Unit | Test conditions |

|-----------------------------------------|-------------------------------|------|------|------|------|-----------------|

| Address setup time                      | t <sub>AS</sub>               | 2    | _    | _    | μs   |                 |

| OE setup time                           | t <sub>oes</sub>              | 2    | —    | _    | μs   |                 |

| Data setup time                         | t <sub>DS</sub>               | 2    | —    | _    | μs   |                 |

| Address hold time                       | t <sub>AH</sub>               | 0    | —    | _    | μs   |                 |

| Data hold time                          | t <sub>DH</sub>               | 2    | _    | _    | μs   |                 |

| OE high to output float delay           | t <sub>DF</sub> <sup>*1</sup> | 0    | _    | 130  | ns   |                 |

| V <sub>PP</sub> setup time              | t <sub>vPS</sub>              | 2    | _    | _    | μs   |                 |

| V <sub>cc</sub> setup time              | t <sub>vcs</sub>              | 2    | _    | _    | μs   |                 |

| CE initial programming pulse width      | t <sub>PW</sub>               | 47.5 | 50.0 | 52.5 | μs   |                 |

| CE setup time                           | t <sub>CES</sub>              | 2    | _    | _    | μs   |                 |

| Data valid from OE                      | t <sub>oe</sub>               | 0    | _    | 150  | ns   |                 |

| CE pulse width during data latch        | t <sub>LW</sub>               | 1    | _    | _    | μs   |                 |

| $\overline{OE} = V_H$ setup time        | t <sub>OHS</sub>              | 2    | _    | _    | μs   |                 |

| $\overline{OE} = V_{H}$ hold time       | t <sub>ohh</sub>              | 2    | _    | _    | μs   |                 |

| Page programming reset time*2           | t <sub>vLW</sub>              | 1    | _    | _    | μs   |                 |

| V <sub>PP</sub> hold time <sup>*2</sup> | t <sub>vrs</sub>              | 1    | _    | _    | μs   |                 |

Notes: 1.  $t_{DF}$  is defined as the time at which the output achieves the open circuit condition and data is no longer driven.

2. Page program mode will be reset when  $V_{\mbox{\tiny PP}}$  is set to  $V_{\mbox{\tiny CC}}$  or less.

#### **Option Page Programming Timing Waveform**

#### Erase

Erasure of HN27C4096AHG/AHCC is performed by exposure to ultraviolet light of 2537 Å and all the output data are changed to "1" after this erasure procedure. The minimum integrated dose (i.e. UV intensity  $\times$  exposure time) for erasure is 15 W · sec/cm<sup>2</sup>.

#### **Mode Description**

#### **Device Identifier Mode**

The device identifier mode allows the reading out of binary codes that identify manufacturer and type of device, from outputs of EPROM. By this mode, the device will be automatically matched its own corresponding programming algorithm, using programming equipment.

#### HN27C4096AH Identifier Code

|                                           |        | A0           | I/O8 – I/O15 | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | I/O0 |          |

|-------------------------------------------|--------|--------------|--------------|------|------|------|------|------|------|------|------|----------|

|                                           | CC-44  | (24)         | (11) – (4)   | (14) | (15) | (16) | (17) | (18) | (19) | (20) | (21) | •        |

| Identifier                                | DG-40A | (21)         | (10) – (3)   | (12) | (13) | (14) | (15) | (16) | (17) | (18) | (19) | Hex data |

| Manufacturer code                         |        | $V_{\rm IL}$ | X            | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 07       |

| Device code                               |        | $V_{IH}$     | X            | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | A2       |

| Notes: 1. $V_{00} = 5.0 \text{ V} + 10\%$ |        |              |              |      |      |      |      |      |      |      |      |          |

Notes: 1.  $V_{cc} = 5.0 V \pm 10\%$

2. A9 = 12.0 V  $\pm$  0.5 V

3. A1 – A8, A10 – A17,  $\overline{CE}$ ,  $\overline{OE} = V_{IL}$

4. ×: Don't care.

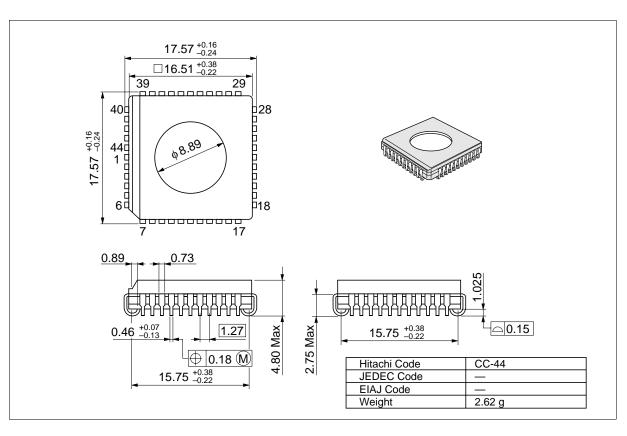

Unit: mm

#### **Package Dimensions**

#### HN27C4096AHG Series (DG-40A)

52.07 53.34 Max 21 40 15.51 Max 14.66 ¢8.89 20 1 1.32 2.54 Min 6.30 Max 15.24 2.54 Max nnnn 0.25-0.05 2.54 ± 0.25  $0.48 \pm 0.10$ 0 – 15° Hitachi Code DG-40A JEDEC Code EIAJ Code SC-615 Mod. Weight 12.57 g

#### Package Dimensions(cont)

#### HN27C4096AHCC Series (CC-44)

Unit: mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## HITACHI

#### Hitachi, Ltd.

Semiconductor & IC Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1835 U S A Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Group Continental Europe Dornacher Straße 3 D-85622 Feldkirchen München Tel: 089-9 91 80-0 Fax: 089-9 29 30 00 Hitachi Europe Ltd. Electronic Components Div. Northern Europe Headquarters Whitebrook Park Lower Cookham Road Maidenhead Berkshire SL6 8YA United Kingdom Tel: 0628-585000 Fax: 0628-778322 Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 0104 Tel: 535-2100 Fax: 535-1533

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsim Sha Tsui, Kowloon Hong Kong Tel: 27359218 Fax: 27306071

## **Revision Record**

| Rev. | Date         | Contents of Modification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Drawn by | Approved by |

|------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|

| 0.0  | May. 6, 1994 | Initial issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | A. Nara  | T. Muto     |

| 1.0  | Apr. 4, 1997 | Change of format<br>DC Characteristics<br>$(V_{cc} = 5 V \pm 10 \%, V_{PP} = V_{SS} \text{ to } V_{CC}, Ta = 0 \text{ to } + 70^{\circ}\text{C})$<br>$I_{CC1} \text{ max } 35 \text{ mA to } 30 \text{ mA}$<br>AC Characteristics<br>Deletion of t <sub>BAC</sub><br>Change of Read timing waveform<br>Deletion of Read timing waveform (Burst access mode)<br>DC Characteristics<br>$(V_{cc} = 6.25 V \pm 0.25 V, V_{PP} = 12.5 V \pm 0.3 V, Ta = 25 ^{\circ}\text{C} \pm 5^{\circ}\text{C})$<br>Change of note2 |          |             |